# III–V Nanowire Transistors for Low-Power Logic Applications: A Review and Outlook

Chen Zhang, Member, IEEE, and Xiuling Li, Senior Member, IEEE

(Review Paper)

Abstract—III-V semiconductors, especially InAs, have much higher electron mobilities than Si and have been considered as promising candidates for n-channel materials for post-Si low-power CMOS logic applications. Combined with the inherent 3-D structure that enables the gate-all-around (GAA) geometry for superb gate electrostatic control, III-V nanowire (NW) MOS-FETs are well positioned to extend the scaling beyond Si. This paper attempts to provide a review of the growth and fabrication approaches (both bottom-up and top-down), and the state-of-the-art device performance of III-V NW GAA MOSFETs, as well as an outlook of their scaling potential.

Index Terms—III-V, gate-all-around (GAA), MOSFET, nanowire (NW), scaling.

# I. INTRODUCTION

-V SEMICONDUCTOR materials, especially InAs, are known to have a much higher electron mobility than Si [1]-[3]. For extremely scaled FETs, the high mobility is translated to high source-side carrier injection velocity [3]-[5]. III-V transistors, therefore, have been widely used for high-speed and RF electronic applications for decades. Record high-frequency performances have been achieved using III-V channels [6]-[8]. Recently, attention has been drawn on the potential of III-V materials for logic device applications [3], [9]-[11], which has historically been the territory of Si. The continuous performance improvement of Si CMOS ICs over the past 40 years has been enabled by aggressive downscaling of the transistor size, as well as the increase of operating frequency, with the enhancement of power density as a side effect. However, as the device packing density increases drastically, the power dissipation has become a major obstacle that prevents further scaling and performance improvement [12], [13]. Replacing Si with other materials possessing higher carrier mobilities, such as III-Vs, could potentially solve the power issue, because a reduced supply voltage  $(V_{dd})$  may be used to deliver similar or even superior

Manuscript received August 16, 2015; revised October 9, 2015; accepted November 3, 2015. Date of publication December 7, 2015; date of current version December 24, 2015. This work was supported by the National Science Foundation under Grant ECCS 1001928 and Grant DMR 1508140. The review of this paper was arranged by Editor W. Tsai.

C. Zhang was with the Electrical and Computer Engineering Department, University of Illinois at Urbana-Champaign, Urbana, IL 61801 USA. He is now with IBM Research, Albany, NY 12203 USA (e-mail: zhangche@us.ibm.com).

X. Li is with the Electrical and Computer Engineering Department, University of Illinois at Urbana-Champaign, Urbana, IL 61801 USA (e-mail: xiuling@illinois.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2015.2498923

device performance [3]. Del Alamo [3] and Chau *et al.* [10] have given detailed discussions of the challenges and opportunities of III–Vs for CMOS applications.

While switching to a new material system is still at the research stage, the industry has already made a revolutionary change in the geometric structure of CMOS channels. Trigate FinFET devices have been adopted by the industry to replace conventional single-gate planar devices. Among all the different multigate structures, the gate-all-around (GAA) nanowire (NW) structure has the shortest natural length (given the same gate oxide thickness and the same lateral dimensions, i.e., the diameter of an NW, the width of a fin, and the thickness of an ultrathin body) and, therefore, the best gate-length scaling potential [14]. A GAA structure will likely be the solution for ultimately scaled transistors. In this light, we here review several important aspects regarding the development of III-V NW nMOSFETs. Section II discusses and compares different growth/fabrication approaches for III-V NW devices. Section III reviews the diameter-dependent band structures of III-V NWs (mainly on binary InAs) as well as their scaling potential. The OFF-state performance is reviewed in Section IV, while the NW electron mobility and the ON-state performance are reviewed and discussed in Section V. Although the scope of this review is limited to nMOS, it is worth noting that one type of III-V materials, InGaSb, has very impressive hole mobilities and can be potentially used for pMOSFET applications [3].

# II. GROWTH/FABRICATION OF III-V NW DEVICES

# A. Bottom-Up, Vertical Vapor-Liquid-Solid Growth

The bottom-up, vapor-liquid-solid (VLS) method, first introduced in [15], is one of the most popular methods for semiconductor NW synthesis. As shown in Fig. 1(a), it utilizes a metal seed particle, usually made of Au, to catalyze and direct the NW growth. Different techniques, including metalorganic chemical vapor deposition (MOCVD), chemical beam epitaxy (CBE), and molecular beam epitaxy, have been used for VLS growth [16]. At certain growth temperature, the seed particle forms with the elements of a semiconductor material (from the vapor phase) a eutectic droplet (liquid phase). As more growth species are introduced, the droplet becomes supersaturated and then the semiconductor material precipitates out in the form of a solid-phase single-crystal NW. In the case of III-V VLS NW growth by MOCVD, trimethylgallium, trimethyl-indium, AsH<sub>3</sub>, and PH<sub>3</sub> are most commonly used precursors. The III-V NWs mostly grow along

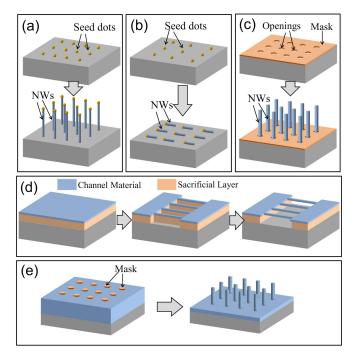

Fig. 1. Schematics of bottom-up and top-down approaches of III-V NW growth/fabrication. (a) Vertical VLS growth. (b) SLE—planar VLS growth. (c) SAE. (d) Top-down planar NWs fabricated by etching the sacrificial layer. (e) Top-down vertical NWs by dry etching.

[111]B direction for energetic reasons [16]. Therefore, vertically aligned NWs can be achieved if a (111) substrate is used [Fig. 1(a)]. VLS growth usually takes place at a temperature much lower than that of the standard thin-film growth such that the thin-film growth, through the vapor–solid (VS) mode, is greatly suppressed. However, the NW growth rate can be high due to the catalytic effect of the seed dots.

The VLS method, as a bottom-up method, holds several distinct advantages. High-aspect ratio NWs with atomically smooth sidewalls and uniform diameters along axial directions can be easily obtained. It is also convenient to scale down the diameter, which is primarily determined by the size of the seed dots. By using colloidal Au dots or metal dots formed through annealing of a thin metal film, VLS InAs NWs with the diameters of less than 20 nm can be readily obtained [17]–[20]. Extremely thin NWs may not grow due to the Gibbs-Thomson effect—loss of supersaturation caused by NW surface energy [21]. However, this does not limit us from obtaining sub-10-nm VLS NW. Jung et al. [22] have recently demonstrated sub-10-nm InAs NWs with a minimum diameter of  $\sim$ 2 nm from Au seeded growth. Ordered NW arrays can be realized by defining Au dots by a lithographical method. Note that due to the formation of hemispherical eutectic droplets, the diameter of the VLS NWs is essentially determined by the volume, instead of the diameter, of the patterned dots (usually having a cylindrical shape) [23]. In this sense, one can reduce the diameter of VLS NWs by only reducing the height of patterned dots, so the lithographical constraint on achieving thin NWs can be relaxed. In addition, heterostuctures along either radial or axial direction can be deterministically incorporated to control the carrier transport property and

subthreshold characteristics [24]–[26]. Axial heterojunctions, e.g., InAs/InAsP axial NWs by CBE [24], can be realized by switching ON/OFF growth precursors during VLS growth. Radial junctions usually require a temperature ramp-up in order to enhance the VS growth [27]. The most attractive potential offered by the VLS method is probably the direct integration of III-Vs on a lattice-mismatched substrate, such as silicon. Due to its unique structure, an NW/substrate heterointerface can accommodate more lattice mismatch when compared with planar thin-film interfaces. Below certain critical diameter [28], high-quality NWs can be grown epitaxially on a foreign substrate without generating axial dislocations. This is particularly attractive considering CMOS requires the integration of both n-channel and p-channel materials (such as InAs and GaSb) on one substrate. III-V NWs, including InAs, which is of great interest for the CMOS application for its extremely high electron mobility, have been epitaxially grown on Si (111) [29]. However, the control of growth directions seems to be still challenging for the direct VLS growth on Si. Since Si has a nonpolar crystal structure with all (111) directions being equivalent (in contrast to polar III-V compound semiconductors where there are  $\langle 111 \rangle A$  and  $\langle 111 \rangle B$  [16]), the growth of III-V NWs on Si (111) could happen both the vertical and three slanted (111) directions [29]. We should note that most VLS studies have been done with Au seed dots, which is not compatible with the Si CMOS technology. CMOS-compatible seeds need to be looked into when we consider direct integration of VLS NWs with Si. It is also worth noting that twinning planes as well as a mix of wurtzite (WZ) and zinc blende (ZB) phases alternating along the axial direction are commonly observed in VLS III–V NWs. The phase purity and the planar defect density can be controlled by growth conditions, such as temperature and V/III ratio [30]-[33].

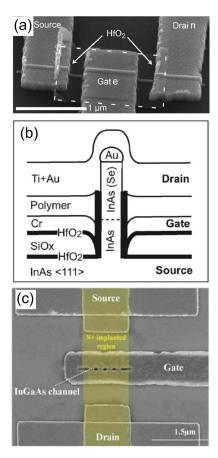

Early proof-of-concept demonstrations of III–V NW transistors are mostly done with VLS NWs [26], [34]. To fabricate a device, vertical NWs were first broken off from the substrate and then randomly dispersed onto an insulating substrate, such as SiO<sub>2</sub>/Si, as shown in Fig. 2(a) adapted from [40]. Although impressive performance was achieved, this method cannot be scaled up for chip-level manufacturing.

A breakthrough was demonstrated by researchers from Lund University. They have developed a nontraditional fabrication scheme to make transistors directly on vertical VLS InAs NW arrays, first on InAs native substrates [35], [36], then on Si [37], [38] (with a relatively thick InAs thin-film buffer layer though). Since the transistor channel is vertical, the key fabrication step is to form spacer layers that can separate source and gate as well as gate and drain. A representative device structure is shown in Fig. 2(b), adapted from [35], where  $SiO_x$  (formed by angled evaporation) was used as the spacer between the source and the gate. The gate length was defined by the thickness of the gate metal which was also deposited by angled evaporation. Before the drain metallization, a polymer spacer was spin-coated and etched back to expose the tip of the NW. With this kind of fabrication method, array-based NW MOSFETs with an NW diameter of sub-30 nm have been realized [37].

Fig. 2. Different device structures of NW MOSFETs. (a) MOSFET device with an InAs NW channel that is broken off from its original substrate and then dispersed onto a foreign substrate (usually SiO<sub>2</sub>/Si). Adapted with permission from [40]. Copyright [2008] IEEE. (b) Vertical VLS NW MOSFETs fabricated by using spacer layers for source/gate and drain/gate separation. Adapted with permission from [35]. Copyright [2008] IEEE. (c) Top–down planar NW MOSFET with p-type NW channels and n<sup>+</sup> implanted S/D. Adapted with permission from [57]. Copyright [2011] IEEE.

Vertically aligned NWs have the potential of achieving a very small transistor footprint. As the top contact is completely isolated from the substrate, the OFF-state leakage current of a vertical NW transistor could be extremely low [39]. The speed performances, however, were shown to be affected by the parasitic capacitances due to large contact pad overlaps [36], [37], [40]. Substantial improvement of RF performance has been shown by using finger contacts to reduce the overlapped area [38]. As the vertical scheme will continue to be developed and assessed by researchers, other challenges include formation of self-aligned source/drain (S/D) (usually achieved in planar devices by S/D implantation or S/D regrowth with gate serving as the mask) and demonstration of its compatibility with even thinner and denser NW arrays. In addition, forming a good ohmic contact directly with the top of the vertical NWs could be challenging as the NWs become even thinner [11] unless a regrown contact region can be developed.

### B. Bottom-Up, Selective Lateral Epitaxy

A new, planar type of VLS growth, where the NWs grow in parallel in the plane of the substrate surface, has recently been discovered in [41]. We call this particular VLS growth selective lateral epitaxy (SLE) where the seed particles provide the selectivity. This is schematically shown in Fig. 1(b). For example, GaAs planar NWs are self-aligned bidirectionally along either [0-11] or [01-1] direction if a (100) substrate is used, while unidirectionally aligned planar NWs can be achieved using (110) substrates [42]. We have found that the planar NW growth directions correspond to the projection of out-of-plane  $\langle 111 \rangle B$  directions (standard VLS directions) on the substrate surface [43] and suggested that this is due to the adhesion between liquid-form seed particles and the substrate [44]. Homogeneous SLE of GaAs planar NW arrays with perfect yield have been demonstrated by defining the Au seed dots lithographically [44]. Remarkably, it has been shown that the planar VLS growth can also be applied to heterogeneous epitaxy. High crystalline quality InAs planar NWs with sub-30-nm width have been directly grown on GaAs (100) substrates despite a huge, 7% lattice mismatch [44].

As a VLS method, the planar NW technology shares similar advantages, such as size downscaling, the incorporation of heterostructures, and the potential for heterogeneous integration. Integrating of n-channel and p-channel NWs can be done by multiple patterned VLS growths. The NWs of the first type can be protected by a growth mask (SiO<sub>2</sub> for example) before the seed particles for the second growth are patterned. In particular, unlike the vertical NWs, the planar VLS NWs are compatible with the well-established planar processing technology. Various types of devices, including MESFETs, MOSFETs, and HEMTs, have been demonstrated on homogeneous GaAs planar NWs [27], [45]-[47]. Decent RF performances measured from the array-based GaAs planar NW HEMTs have been reported [48]. For those devices based on homogeneous GaAs planar NWs, the device structure resembles that of a standard planar device except an inherent trigate structure, including the top and two sidewall facets of an NW (the bottom is attached to the substrate).

For the heterogeneous InAs planar NWs grown directly on GaAs, we have developed a method to fabricate GAA NW MOSFETs by releasing the NW channel from the substrate [49]. Due to the competing VS mode during the VLS NW growth, the as-grown InAs planar NW sample [schematically shown in Fig. 1(b)] could be covered by a thin layer of InAs parasitic film across the entire surface. For GaAs planar NWs, the parasitic growth has been minimized to practically zero by optimizing the growth conditions [27], while the current stage of InAs planar growth development left a ~2-nm-thick parasitic InAs film. In order to perform the undercut etching to release the NW channel, this parasitic InAs film was precisely removed by the digital etching method, which will be explained in more details in Section II-D. The NW channel was then released by selectively etching the exposed GaAs from InAs by a NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O solution. The parasitic film on the S/D region was intentionally kept for improving the contact resistance, which resembled a regrown S/D. The angled sputtering was used to form a conformal gate metal contact. The final device structure is somewhat similar to that of the planar NW MOSFETs fabricated by the top-down etching approach [Fig. 2(c)].

Heterogeneous SLE is a promising technology as it benefits from both bottom—up growth and top—down planar processing technology. Yet it still remains to be shown if it can be done directly on Si, a more desired platform for device integration. Ternary NWs should also be feasible by SLE, where the challenge lies in finding a growth condition that favors the inplane orientation at the same time allows independent control of the incorporation of two anions or cations. Extensive efforts on growth optimization will be required.

#### C. Bottom-Up, Selective-Area Epitaxy

The selective-area epitaxy (SAE) approach also produces vertically aligned NW arrays. In contrast to VLS method, it does not rely on any metallic seed dots to guide the growth. Instead, it uses an amorphous mask, usually made of SiO<sub>2</sub>, to prevent nucleation on the unwanted area. Small pores are opened on the mask by a lithographical method to expose the surface of the semiconductor substrate underneath, usually of (111) orientation. The vertical NWs grow out of the pores, as shown in Fig. 1(c), and no materials are deposited on the area protected by the mask. In fact, the SAE method has been a long-standing topic for optoelectronic applications [50]. Recently, it has been used to produce vertical NWs for transistor applications [51]–[53]. The SAE growth usually happens in an MOCVD system in order to maintain good growth selectivity and at a growth temperature similar to those of the standard thin-film growth. The diameter of SAE NWs has been shown to be primarily determined by the size of the pore [54], for which the scaling is limited by lithography.

As a bottom-up method, SAE growth shares with the VLS method similar challenges, as well as the advantages, including the heterogeneous integration of lattice-mismatched materials and the flexibility in the incorporation of heterostructures in NWs. In fact, SAE growth of high-In-content InGaAs NWs directly on Si appears to be more successful. The growth of vertically aligned high-yield In<sub>0.7</sub>Ga<sub>0.3</sub>As [51] and InAs NW arrays [55] on Si (111) substrates have been realized, demonstrating a significant potential for heterogeneous integration. The high yield was enabled by forming As terminated Si<sup>3+</sup> surface prior to NW growth. It was found that the huge lattice mismatch (11.6% between InAs and Si) was fully accommodated by the misfit dislocations confined at the heterogeneous interface, resulting in a high-quality, relaxed InAs NW body [55]. In addition, an HEMT-like coreshell structure has been applied to those vertical SAE NWs, leading to a clear improvement of carrier transport characteristics [51]. One important issue of SAE III-V NWs is that the as-grown NWs show strong WZ-ZB polytypism resulting in a large density of stacking faults, which could act as scattering centers. Unlike the VLS method where growth conditions can be tuned to grow phase-pure NWs, stacking-fault-free SAE NWs have not been demonstrated.

The fabrication process of the vertical SAE NW transistors is very similar to that of the VLS NWs. Therefore, the device structure is similar to Fig. 2(b). Yet there are a few reports showing the growth and devices of sub-50-nm NWs by an

SAE method, presumably limited by the available lithography technology in an academic institute.

#### D. Top-Down Approaches

The top-down approach for fabricating III–V NW structures usually starts with a multilayer thin-film structure having a bottom sacrificial layer, which can be selectively etched away in order to release the NWs [56]-[59]. Because of the wellestablished III-V material system, many selective etchants are known. For example, high Al content AlGaAs can be selectively etched from GaAs by hydrofluoric acid. HCL etches InP but does not attack most other III-V materials, such as InGaAs. Fig. 1(d) shows a generic fabrication process for top-down planar III-V NWs, which was first demonstrated in [57] on an InGaAs/InP structure where the InP substrate served as the sacrificial layer. First, a thin-film heterostructure with the sacrificial layer at the bottom and the channel layer on the top is epitaxially grown. The substrate itself can be the sacrificial layer if a selective etchant can be found. Then, finlike structures can be defined as dry etching, and NWs are formed by etching away the supporting sacrificial layer. Note that since the wet etching is usually anisotropic, the NW orientation can be chosen to facilitate the undercut etching for NW release [57]. An example of the top-down planar NW device structure is shown in Fig. 2(c), adapted from [57]. The InGaAs NWs are p-type doped (during the thin-film growth), whereas the S/D is heavily n-typed doped by ion implantation. Note that although the gate metal contact appears to be wide, the real channel length is defined as the gap between the implanted source and drain areas.

The top-down approach has the advantage of being readily applicable to large-scale manufacturing. Technologies, such as ion implantation and S/D regrowth, can be easily applied. Applying strain for mobility enhancement should also be straightforward. As fabricated from thin films, etched NWs do not contain twining defects or ZB-WZ polytypism, which could be present in bottom-up NWs. In addition, by growing multiple channel/sacrifice layers, vertically stacked NW array could be achieved, creating a new dimension for planar channel integration [59]. As the top-down approach relies on the thin-film growth, this could impose a limit on obtaining very high-In-content InGaAs due to their huge lattice mismatch with the common III-V substrates—GaAs and InP. A thick metamorphic buffer may be used, but it greatly adds the complexity. It is also not so clear how the top-down NWs can be effectively integrated on Si side-by-side with p-channel devices for CMOS applications. In addition, dryetching-induced surface damage may degrade the transport property.

Recently, top-down chloride-based dry etching was used to produce vertical InGaAs NWs that are similar to those formed by bottom-up growth approaches [60], [61]. NWs as thin as 15 nm have been fabricated by this approach [61]. A schematic is shown in Fig. 1(e), and the device structure resembles that of a bottom-up vertical NW device. The so-called digital etching was used to reduce the surface damage induced by dry etch [60], [61]. The digital etch is a very

precise etching method. Each cycle of digital etch consists of a room-temperature oxidation followed by an oxide removal process. The oxidation, which can be done in an oxygen plasma asher [62] or in a UV ozone tool [63] or by H<sub>2</sub>O<sub>2</sub> [64], is a self-limiting process that stops at about 1–1.6 nm beneath the surface depending on the material. Therefore, each etching cycle can precisely remove a very thin layer of material. This is potentially very useful for future fabrication of III–V nanostructures, for example, to precisely thin down the NWs.

#### III. BAND STRUCTURE AND SCALING POTENTIAL

As the gate length of MOSFETs is scaled below 30 nm [65], the diameter of an NW channel, as required by the scaling laws, also has to be in nanoscale. The natural length  $(\lambda)$  that characterizes the scaling behavior of a GAA cylindrical NW structure, given by [66], is

$$\lambda = \sqrt{\frac{2\varepsilon_s d^2 \ln(1 + 2t_{\text{ox}}/d) + \varepsilon_{\text{ox}} d^2}{16\varepsilon_{\text{ox}}}}$$

(1)

where  $\varepsilon_s$ ,  $\varepsilon_{ox}$ ,  $t_{ox}$ , and d are the dielectric constant of the semiconductor NW, the dielectric constant of the oxide, the thickness of the oxide, and the diameter of the semiconductor NW, respectively. The short-channel effect will be negligibly small if the gate length,  $L_g$ , is more than six times larger than  $\lambda$  [14]. If  $L_g = 20$  nm, EOT = 0.6 nm and assuming an InAs channel with  $\varepsilon_s = 15.1\varepsilon_0$ , the diameter of the NW needs to be smaller than  $\sim 10$  nm in order to ensure a good short-channel performance. It is important to understand how the band structures change as the diameter enters the sub-10-nm scale as it is directly related to the threshold voltage shift [67]. Within this size range, III-V NWs are supposed to show clear quantum confinement effect due to their small effective masses. A minimum tolerable d of In<sub>0.53</sub>Ga<sub>0.47</sub>As NWs is estimated to be 9 nm in [67] by effective mass approximation considering an acceptable threshold voltage variation of 100 mV induced by the processing variation of NW diameter. In an NW channel, a simple estimation by the effective mass approximation of the bandgap increase  $\Delta E_g$  due to quantum confinement is [68]

$$\Delta E_g = E_g(d) - E_{g,\text{bulk}} = 2.34 \frac{\pi^2 \hbar^2}{2d^2 m_e^*}$$

(2)

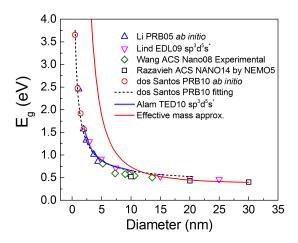

where  $m_e^*$  is the electron effective mass  $(0.023m_0)$  for InAs) and the contribution from the valence band is left out due to the large heavy hole effective mass in III–Vs  $(0.41m_0)$  for InAs). For InAs NWs, interestingly, both the theoretical calculations [20], [69]–[72] and the experimental results [68] have shown that the effective mass approximation greatly overestimates  $\Delta E_g$  for d < 10 nm. This deviation was attributed to the strong conduction band nonparabolicity in InAs.

Fig. 3 summarizes both theoretical and experimental results on the bandgap of InAs NWs with respect to diameter. As shown in Fig. 3, the effective mass approximation gives a very good estimation of bandgap for d>15 nm, but fails to follow the results calculated by more advanced ab initio and  $sp^3d^5s^*$  methods. For d<10 nm,

Fig. 3. Summary of theoretical and experimental results on the bandgap of InAs NWs as a function of diameter. The  $E_g$  value of bulk InAs is 0.354 eV.

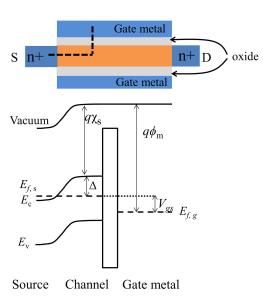

Fig. 4. Schematic of a long-channel NW MOSFET with highly doped source and drain regions. The channel is undoped or lightly doped. Shown at the bottom is the band diagram along the dashed line drawn on the device diagram. The MOSFET is biased in subthreshold.

dos Santos and Piquini *et al.* [72] fitted their *ab initio* data and the experimental results from [68] to yield

$$\Delta E_g = \frac{1.94}{d^{0.81}} \text{ (eV)}.$$

(3)

Here, the increase in bandgap follows  $d^{-0.81}$  instead of the more aggressive  $d^{-2}$ .

Fig. 4 shows the band diagram along the dashed line drawn on the schematic of a long-channel undoped NW MOSFET biased in the subthreshold regime. Following [67] and [73], the bands are essentially flat inside the channel, and no potential drops across the gate oxide, because the mobile charges are negligible in subthreshold (interface-trap charges are not considered). Therefore, the gate voltage  $V_{\rm gs}$  can be written as

$$V_{\rm gs} = \frac{1}{q} (E_{f,s} - E_{f,g}) = \phi_m - \chi_s - \frac{\Delta}{q}$$

(4)

where  $E_{f,s}$  and  $E_{f,g}$  are the Fermi levels of source and gate, respectively.  $\phi_m$  is the gate metal work function,  $\chi_s$  is the electron affinity of the channel semiconductor, and  $\Delta$  is the distance between source Fermi level and the conduction band minimum of the channel. Due to the diameter-dependent quantum confinement effect,  $\chi_s$  can be written as

$$\chi_s = \chi_0 - \frac{\delta E_c(d)}{q} \tag{5}$$

where  $\chi_0$  is the bulk electron affinity and  $\delta E_c(d)$  is the displacement of the conduction band minimum in an NW, which is approximately  $\Delta E_g$  for III–Vs. Therefore, (4) becomes

$$V_{\rm gs} = \phi_m - \chi_0 - \frac{\Delta}{q} + \frac{\delta E_c(d)}{q}.$$

(6)

If we define certain  $\Delta$  to be the threshold condition, the threshold voltage increase due to the diameter downscaling is approximately

$$\Delta V_{\rm gs}(d) = \frac{\delta E_c(d)}{a}.$$

(7)

Note this is a simplified derivation and the result of the more rigorous charge-based analysis can be found in [67]. However, the difference has a very small effect on the analysis below.

Following [67], we calculate for InAs NWs the minimum allowed d limited by the threshold voltage variation due to process variation of d. Similarly as in [67], it is assumed that d has a process variation of  $\pm 10\%$  and a criteria of  $\Delta V_{\rm gs} < 100$  mV. Using (3), we calculate the minimum tolerable diameter,  $d_{\rm min}$ , of InAs NWs is 4.1 nm. If we further assume a 0.6-nm equivalent oxide thickness (EOT) ( $\sim 3.85$ -nm HfO<sub>2</sub>), the natural length  $\lambda$  is calculated to be 1.55 nm and, therefore, a minimum gate length  $L_{g,\rm min}$  (=6 $\lambda$ ) of  $\sim$ 9 nm for negligible short-channel effect. This shows a good scaling potential for sub-10-nm node technologies [65]. Note that if the effective mass approximation is used for  $\delta E_c$ ,  $d_{\rm min}$  and  $L_{g,\rm min}$  are larger, being 12.4 and 23.4 nm, respectively. Although the scaling limit analysis above as proposed in [67] is well accepted, it can possibly be overcome as the processing technology advances.

# IV. SUBTHRESHOLD PERFORMANCE AND INTERFACE-TRAP DENSITY

A close-to-ideal subthreshold slope (SS = 60 mV/decade) is desired for modern MOSFETs to achieve low static power dissipation. However, for III–V materials, the interface-trap density  $D_{\rm it}$  (eV<sup>-1</sup>cm<sup>-2</sup>) at the oxide–semiconductor interface is usually very high, and it degrades the subthreshold performance. Because of the presence of interface traps, (4) needs to be modified to consider the potential drop across the oxide due to interface charges  $Q_{\rm it}$  (C/cm)

$$V_{\rm gs} = \phi_m - \chi_s - \frac{\Delta}{q} - \frac{Q_{\rm it}}{C_{\rm ox}}$$

(8)

where  $C_{\text{ox}}$  (F/cm) is the oxide capacitance per unit length along an NW, which can be written as, for the singe-layer oxide

$$C_{\text{ox}} = \frac{2\pi \,\varepsilon_{\text{ox}}}{\ln(1 + 2t_{\text{ox}}/d)}.\tag{9}$$

In the case of multilayer oxides

$$[C_{\text{ox,tot}}]^{-1} = \frac{\ln(1 + 2t_{\text{ox},1}/d)}{2\pi \,\varepsilon_{\text{ox},1}} + \frac{\ln(1 + 2t_{\text{ox},2}/(d + 2t_{\text{ox},1}))}{2\pi \,\varepsilon_{\text{ox},2}} + \cdots$$

(10)

Since the drain current  $I_{\rm ds}$  is proportional to the mobile charges density,  $Q_n$ , near the source which equals  $qN_c \exp(-\Delta/kT)$  [74], it is straightforward to conclude from (8) that, for a long channel device  $(L_g > 6\lambda)$ , SS (mV/decade) defined as  $dV_{\rm gs}/d(\log_{10}I_{\rm ds})$  can be written to be (similarly as in [75] but considering a cylindrical structure)

$$SS = 60 \cdot \left(1 + \frac{1}{C_{\text{ox}}} \frac{dQ_{\text{it}}}{d(\Delta/q)}\right) \approx 60 \cdot \left(1 + \frac{q\pi dD_{\text{it}}}{C_{\text{ox}}}\right). \quad (11)$$

Therefore, (11) provides a convenient way to estimate  $D_{\rm it}$  in a long-channel NW MOSFET. However, we should also note that the other factors that could affect SS are not considered in (11). Other method for  $D_{\rm it}$  extraction, such as C-V measurements, cannot be easily implemented on an NW device, especially single-NW transistors.

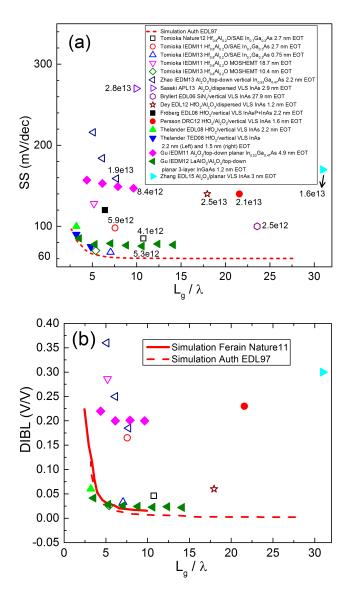

Fig. 5(a) summarizes SS from the III–V NW MOSFET works [18], [24], [35], [40], [47], [51], [53], [57], [58], [60], [76]–[79]. The SSs are plotted against the ratio between the gate length  $L_g$  and the natural length  $\lambda$ , which is calculated by (1). In the case of multilayer oxide, it can be shown by following the original derivation in [66] that:

$$\lambda = \sqrt{\frac{\pi \,\varepsilon_{\rm s} d^2}{4 C_{\rm ox,tot}} + \frac{d^2}{16}}.$$

(12)

For devices with the MOSHEMT structure, the barrier semiconductor layers are also considered in the calculation of  $C_{ox}$ . Relative dielectric constants of 8 [80] and 18 [81] are used for ALD Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, respectively, to obtain EOT. The simulated SS versus  $L_g/\lambda$  taken from [66] (without  $D_{\rm it}$ ) is also shown in Fig. 5(a) for a comparison with the experimental data. As seen from Fig. 5(a), many experimental data do not follow the simulated results, showing a much higher SS due to high Dit. Al2O3 has been the most popular dielectric material for III-V MOS devices after high-performance MOSFETs were demonstrated [82], [83]. Dit estimated by (11) for the top-down etched vertical Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As NW devices [60] is  $1.9 \times 10^{13} \text{ eV}^{-1}\text{cm}^{-2} \cdot (\text{NH}_4)_2\text{S}$  solution has been widely used for III-V MOS device interface passivation [84], [85]. With (NH<sub>4</sub>)<sub>2</sub>S passivation, D<sub>it</sub> is estimated to be in the middle  $10^{12} \text{ eV}^{-1}\text{cm}^{-2}$  range from the top-down planar InGaAs NW devices [58], [59]. Forming gas annealing, a standard approach used to improve the Si/SiO<sub>2</sub> interface, has also been shown effective in improving the Al<sub>2</sub>O<sub>3</sub>/InGaAs NW interface quality [75]. On InAs bottom-up VLS NWs, both Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> [18], [24], [77], [79] yield a D<sub>it</sub> great than  $2 \times 10^{13} \text{ eV}^{-1} \text{cm}^{-2}$  based on (11). Interestingly, plasma-enhanced chemical vapor deposited (PECVD) SiN<sub>x</sub> seems to form a better interface with InAs NWs with an estimated  $D_{\rm it}$  of 2.5  $\times$  10<sup>12</sup> eV<sup>-1</sup>cm<sup>-2</sup> [78]. Surprisingly, SAE NW devices do not show much degraded  $D_{it}$  (~4 ×  $10^{12} \text{ eV}^{-1}\text{cm}^{-2}$  extracted from [51]) compared with the other types of NWs, although SAE NWs do not have a welldefined sidewall facet due to the presence of high-density

Fig. 5. (a) Plot of SS versus  $L_g/\lambda$ . SS values are taken from experimental results of III–V NW MOSFETs in the literature. Extracted  $D_{\rm it}$  numbers in unit of cm<sup>-2</sup>eV<sup>-1</sup> have been marked next to long-channel data points. Red dashed line: trend for simulated GAA NW transistors taken from [66]. (b) Plot of experimental DIBLs of III–V NW MOSFETs versus  $L_g/\lambda$ . The symbols in (b) share the same legend as (a). The lines are simulated DIBL data from [14] and [66].

stacking faults. Nonetheless, all those interface-trap densities extracted from NW devices are somewhat larger than the best results from planar devices where a midgap  $D_{\rm it}$  in the middle  $10^{11}~{\rm eV^{-1}cm^{-2}}$  range can be achieved [80], [86]. This is presumably related to the difficulty of simultaneously passivating multiple facets that are present in an NW structure. According to [90], the interface properties can be inherently different for different III–V surface orientations given the same oxide material. The GaAs (111)A surface, which is the sidewall facet of the bottom–up planar VLS NWs [46], has been shown to be free of Fermi-level pinning and yield the best MOS interface quality compared with the other surfaces [90]. Given a high  $D_{\rm it}$ , EOT needs to be reduced such that  $C_{\rm ox}$  is much larger than the capacitance induced by interface

traps to get a close-to-ideal SS (11). For example, assuming  $D_{\rm it} = 5 \times 10^{12} \ {\rm eV^{-1}cm^{-2}}$ , an EOT of less than  $\sim 0.8$  nm can lead to SS of sub-70 mV/decade for long-channel devices. As seen from Fig. 5(a), devices with thin EOTs generally follow the ideal curve more closely.

Two passivation schemes are worth noting here. One is to utilize a radial III-V heterojunction structure. For example, InP, a relatively high-bandgap material in the III-V family, was shown to form a better oxide/semiconductor interface than InGaAs [86].  $D_{it}$  in the low  $10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> range has been demonstrated [86]-[88]. By inserting a thin layer of InP between the gate oxide and the high-mobility InGaAs, the interface quality is expected to be improved. This has been shown in comparative studies on planar devices [89] and also on NWs [26]. Note that an epitaxially smooth interface is desired between InP and InGaAs, so it is preferred that the InP deposition is done monolithically after the NW growth. Bottom-up VLS and SAE technologies are, therefore, better suited for this passivation scheme. Another interesting technology is to use a Si interlayer between the oxide and III-Vs to improve the interface quality. This Si interlayer has been shown to be effective to unpin the GaAs surface Fermi level on both (100) and (111)B surface [91]-[93]. The oxide/Si/InGaAs interface also exhibited a low D<sub>it</sub> [94]. The Si interlayer is usually deposited by PECVD and has been shown to be effective in removing oxygen from the native Ga<sub>2</sub>O<sub>3</sub> [95], which is believed to be responsible for the Fermilevel pinning in the upper half of the GaAs bandgap [90]. This kind of ex situ passivation scheme is attractive due to its simplicity and potential for cost-efficient large-scale manufacturing. Although Si interlayer was shown to be effective on GaAs NWs [46], its effectiveness is still to be demonstrated on high-In-content InGaAs NWs.

Fig. 5(b) shows a summary of drain-induced barrier lowering (DIBL) versus  $L_g/\lambda$  in the literature. The symbols share the same legend, as shown in Fig. 5(a). How  $D_{\rm it}$  affects DIBL is not so clear as SS and requires some simulation studies. However, we observe from Fig. 5(b) that, in general, a device with low  $D_{\rm it}$  [estimated from Fig. 5(a)] and thin EOT follows the ideal curve better

# V. MOBILITY AND ON-STATE PERFORMANCE

As III–Vs are primarily of interest for their high electron mobility, it is, therefore, very important to examine how the mobility can be preserved in an NW structure, especially how the mobility changes as diameter decreases. The low-field mobility (will hereafter be referred as just mobility) is not only interesting for the fundamental transport study, but it also important for predicting the drain current in short-channel devices. It is directly related to the carrier backscattering coefficient, and the higher it is, the closer a MOSFET device approaches its ballistic limit [96]. Most detailed mobility studies of III–V NWs are based on a VLS method [19], [26], [97]–[101], due to its convenience for preparing NWs with a wide range of diameters and, with several microns in length, which ensures the carrier transport is in the diffusive regime. For the VLS-NW mobility study, back-gated MOSFET devices

with NWs sitting on a SiO<sub>2</sub>/Si substrate are commonly used. The so-called field-effect mobility ( $\mu_{\rm FE}$ ) is often extracted from the measured transconductance  $g_m$

$$\mu_{\text{FE}} = \frac{g_m L_g}{V_{\text{ds}} C_g} \tag{13}$$

where  $C_g$  is the total gate capacitance and  $V_{\rm ds}$  needs to be small to ensure a low-field condition. Because the thickness of SiO<sub>2</sub> used for the backgate is commonly more than 50 nm in those works mentioned above, the geometric oxide capacitance,  $C_{\rm ox}$ , is small compared with the ON-state semiconductor capacitance,  $C_s$ . So  $C_g$  is oftentimes approximately replaced by  $C_{\rm ox}$ . It is worth noting that  $D_{\rm it}$  is not considered in those works, so the gate capacitance is somewhat overestimated considering that only free carriers can contribute to the current.

The measurements on the VLS InAs NWs showed a trend where  $\mu_{FE}$  decreases as the NW diameter, d, reduces [19], [97], [99]. A room-temperature peak  $\mu_{\rm FE}$  of  $\sim$ 6000 cm<sup>2</sup>/V·s was measured for d = 35 nm, and it reduced to  $\sim 2500 \text{ cm}^2/\text{V} \cdot \text{s}$  for d = 15 nm [19]. These numbers are to be compared with  $\sim 30\,000$  cm<sup>2</sup>/V·s measured from planar AlSb/InAs quantum wells [102]. The decrease was attributed to the surface roughness scattering as any surface effect would be more pronounced for thinner NWs. Similar trend was also observed in In<sub>0.7</sub>Ga<sub>0.3</sub>As NWs [98]. Wang et al. [97] also observed a monotonic decrease of peak  $\mu_{FE}$  when d reduced from  $\sim$ 55 nm to  $\sim$ 22 nm. In addition, they systematically studied the surface roughness effect for a fixed diameter. The sidewall surface rms roughness was measured by atomic force microscopy on NWs that were laid down laterally. It was shown that for NWs with the diameters of ~27 nm, roomtemperature peak  $\mu_{FE}$  decreases from  $\sim$ 8200 cm<sup>2</sup>/V · s with rms  $\approx 0.86$  nm to  $\sim 1200$  cm<sup>2</sup>/V·s with rms  $\approx 1.87$  nm. Note that all the above measurements used as-grown NWs covered with a native oxide layer of a couple of nanometers. Gupta et al. [100] observed a similar trend for the diameter-dependent mobility in InAs NWs but claimed that surface state scattering, instead of roughness, dominated in their case.

Interestingly, the diameter-dependent mobility has a different trend observed in the well-passivated InGaAs NWs [101], [103]. A high-quality, directly interfaced oxide material or other high-bandgap III-Vs can push the peak of the carrier concentration away from the interface due to a quantum mechanical effect. This could potentially help the mobility improvement. On the other hand, it is questionable if a low-quality native oxide layer could have such an effect. Gu et al. [103] observed an increase of the effective electron mobility in their top-down In<sub>0.53</sub>Ga<sub>0.47</sub>As NW MOSFETs when the NW width decreases from 50 to 30 nm. They explained the result by the carrier volume inversion. According to their simulation, electrons in a 30-nm-thick NW tends to concentrate more in the center of the NW compared with 50-nm NWs, presumably resulting in a reduced surface effect. Van Tilburg et al. [101] also observed an increase of mobility as d reduced in their InAs NWs passivated by a thin InP shell layer, which was monolithically grown after the NW growth. A remarkably high  $\mu_{\rm FE}$  of 11500 cm<sup>2</sup>/V · s was measured from a similar InAs/InP core/shell structure (d = 25 nm)

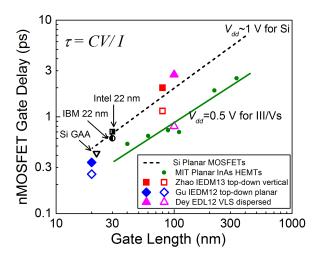

Fig. 6. CV/I gate delays of selected, representative III–V NW MOSFETs [18], [58], [60]. The delays of Si MOSFETs and the state-of-the-art planar III–V devices are also shown (the data are taken from [106]). The open symbols represent the delay calculated by the gate capacitance that rules out the contribution from interface traps, whereas the filled symbols are with  $D_{\rm if}$ .

in [26] at room temperature. Those results demonstrate an HEMT-like heterostructure a very attractive method for improving the carrier mobility in III–V NWs. Although the surface-related mobility degradation may eventually take over for extremely scaled NWs, the experimental results above suggest that a well-passivated NW might push the surface-effect-dominated size range toward the smaller end. Overall, the measured mobilities in InAs and InGaAs NWs are substantially higher than those in the inversion layer of a Si MOSFET (typically in the range of several hundred in cm²/V · s [74]) and those measured from Si NW GAA MOSFETs [104].

Fig. 6 shows the gate delay of the high-performance, representative III-V NW devices calculated by  $C_g V_{dd}/I_{dsat}$  (will be referred to CV/I hereafter) [9]. Note that the CV/I delay can be considered intrinsic as it does not consider the parasitic parameters, such as the fringing capacitance. Furthermore, an effective current  $I_{\text{eff}}$ , which is smaller than  $I_{d\text{sat}}$ , was shown to give a better estimation of the gate delay [105]. Therefore, CV/I gives a very optimistic estimation. Nonetheless, it is still a useful metric to compare the potential of different technologies as it has been used in [9] and [106]. The CV/Idelays of Si MOSFETs of a wide range of technology nodes as well as the delays of the planar InAs HEMT devices are also shown in Fig. 6. Both sets of data are taken from [106].  $V_{\rm dd}$  of the Si data is ~1 V. In addition, the delays of the advanced Intel 22-nm node ( $V_{\rm dd} = 0.8 \text{ V}$ ) [108] and IBM 22-nm node ( $V_{dd} = 1 \text{ V}$ ) [109] are calculated and highlighted. The state-of-the-art Si GAA NW MOSFET is also shown [110]. Note that as seen from Fig. 6, the state-of-the-art planar III-V devices have shown a clear advantage in intrinsic delay, remarkably, at a low  $V_{\rm dd}$  of 0.5 V.

Following [9], because III–V devices normally do not have an optimized threshold voltage  $V_{\rm th}$ ,  $I_{\rm dsat}$  is taken at  $V_{\rm ds} = V_{\rm dd}$  and  $V_{\rm gs} = V_{\rm th} + (2/3)V_{\rm dd}$ , where  $V_{\rm dd}$  is 0.5 V. The gate capacitance,  $C_{\rm g}$ , is obtained from a 2-D Poisson–Schrödinger

$\label{eq:table I} \text{TABLE I}$   $I_{\text{ON}}$  Comparison Between III–V and Si NW Devices

|        | d<br>(nm) | L <sub>g</sub> (nm) | Method   | I <sub>on</sub> <sup>a</sup><br>(μΑ/μm) | Ref.  |

|--------|-----------|---------------------|----------|-----------------------------------------|-------|

| Si     | 12.8      | 22                  | Top-down | 550 <sup>ь</sup>                        | [110] |

| InAs   | 15        | 100                 | VLS      | 400                                     | [18]  |

| InGaAs | ~25       | 20                  | Top-down | 500                                     | [58]  |

<sup>&</sup>lt;sup>a</sup>  $I_{on}$  is normalized to total perimeter and estimated at  $V_{ds} = V_{dd} = 0.5 \text{ V}$  and  $V_{gs} = V_{th} + (2/3)V_{dds}$ , where  $V_{th}$  is extracted from peak  $g_m$  method.

coupled simulation of the gate electrostatics at the NW cross section by Nextnano [107].  $D_{\rm it}$ , as estimated earlier, is added to capture the gate voltage stretch-out. Note that two data points are shown for each NW device in Fig. 6. The open symbols represent the delay calculated by the gate capacitance that rules out the contribution from interface traps, whereas the filled symbols are with  $D_{\rm it}$ . As we can see, the open symbols follow better with the trend of the state-of-the-art planar III–V devices (those are HEMT devices that do not have  $D_{\rm it}$  effect) and show advantage over the Si MOSFETs. However,  $D_{\rm it}$  is seen to substantially corrupt the gate delay as it increases the total gate capacitance and also degrades current, because a substantial portion of channel electrons go to interface states, and therefore does not conduct current.

As the CMOS scaling continues, the parasitic and wiring capacitances have become increasingly significant such that the intrinsic gate capacitance is now not dominating. Therefore, it will also be informative to compare ON-state current at fixed  $V_{dd}$ . Simulation results have shown that III-V NW devices (especially InAs) do not outperform Si when both operate at their ballistic limit [111]. The reason is that III-Vs have small electron effective mass leading to reduced density of states and, therefore, reduced gate capacitance and inversion charge. Nonetheless, the state-of-the-art planar III-V devices [106], [112] show considerably higher I<sub>ON</sub> compared with the advanced Si FinFET technology [113] when  $I_{ON}$  (at  $V_{dd} = 0.5$  V and  $I_{OFF} = 100$  nA/ $\mu$ m) is normalized to the actual conducting width. III-V planar devices now operate very close to the ballistic limit [114], while Si devices do not. It is arguable if Si devices can eventually reach the ballistic limit. Those experimental results encourage the continuous research on III-V device, including NWs, for CMOS applications. Table I compares  $I_{ON}$  of the best III-V NW MOSFETs to the state-of-the-art Si GAA NW device. Currently, for experimental results, III–V NWs have not shown an advantage over Si in terms of drive current. Further enhancement of current would require a significant improvement of NW/high-k interface quality to both reduce  $D_{it}$  and increase mobility.

# VI. CONCLUSION

In summary, we have reviewed various aspects of the development of III–V NW transistors. Advantages and challenges of each fabrication approach have been discussed. Although the top–down methods have been prevailing in the industrial manufacture, the bottom–up methods have been developed to a

point that is worth some seriously considerations for practical use, given their potential in the heterogeneous integration and convenience for *in situ* passivation through heterostructures. The InAs NWs have been shown to have a very good scaling potential for beyond-10-nm technology node. Despite so, III–V NW MOSFETs with a sub-10-nm diameter still remain to be extensively studied by experiment. High oxide–semiconductor interface-trap density, a long-standing historical problem for III–Vs, still greatly affects both the OFF-state and ON-state performance of III–V NW transistors. Surface passivation by forming an abrupt heterostructure with some other higher bandgap semiconductors, such InP, is highlighted here as a very promising technology for both reducing  $D_{it}$  and improving the carrier transport property.

An NW GAA structure is of interest primarily due to its superb gate electrostatics that can allow further gate-length scaling. Yet the speed performance could be affected, because the NW architecture tends to have an increased ratio between the parasitic capacitance and the useful gate capacitance [104]. Note that the parasitic capacitances usually do not scale with the gate length. New innovations in design and processing technologies for maximizing the speed performance of NW transistors are needed in the future development.

#### ACKNOWLEDGMENT

X. Li would like to thank Prof. J. del Alamo for his insightful comments and critical reading of this paper.

#### REFERENCES

- D. Chattopadhyay, S. K. Sutradhar, and B. R. Nag, "Electron transport in direct-gap III–V ternary alloys," *J. Phys. C, Solid State Phys.*, vol. 14, no. 6, pp. 891–908, 1981.

- [2] T. P. Pearsall and J. P. Hirtz, "The carrier mobilities in Ga<sub>0.47</sub>In<sub>0.53</sub>As grown by organo-mettalic CVD and liquid-phase epitaxy," *J. Crystal Growth*, vol. 54, no. 1, pp. 127–131, 1981.

- [3] J. A. del Alamo, "Nanometre-scale electronics with III–V compound semiconductors," *Nature*, vol. 479, no. 7373, pp. 317–323, Nov. 2011.

- [4] D.-H. Kim, J. A. del Alamo, D. A. Antoniadis, and B. Brar, "Extraction of virtual-source injection velocity in sub-100 nm III–V HFETs," in IEDM Tech. Dig., 2009, pp. 35.4.1–35.4.4.

- [5] T.-W. Kim and J. A. del Alamo, "Injection velocity in thin-channel InAs HEMTs," in *Proc. Compound Semiconductor Week, 23rd Int. Conf. Indium Phosph. Rel. Mater.*, 2011, pp. 1–4.

- [6] D.-H. Kim, J. A. del Alamo, P. Chen, W. Ha, M. Urteaga, and B. Brar, "50-nm E-mode In<sub>0.7</sub>Ga<sub>0.3</sub>As PHEMTs on 100-mm InP substrate with f<sub>max</sub> > 1 THz," in *IEDM Tech. Dig.*, 2010, pp. 30.6.1–30.6.4.

- [7] E.-Y. Chang, C.-I. Kuo, H.-T. Hsu, C.-Y. Chiang, and Y. Miyamoto, "InAs thin-channel high-electron-mobility transistors with very high current-gain cutoff frequency for emerging submillimeter-wave applications," *Appl. Phys. Exp.*, vol. 6, no. 3, p. 034001, Mar. 2013.

- [8] D.-H. Kim, B. Brar, and J. A. del Alamo, " $f_T = 688$  GHz and  $f_{max} = 800$  GHz in  $L_g = 50$  nm  $In_{0.7}Ga_{0.3}As$  MHEMTs with  $g_{m\_max} > 2.7$  mS/ $\mu$ m," in *IEDM Tech. Dig.*, 2011, pp. 13.6.1–13.6.4.

- [9] R. Chau et al., "Benchmarking nanotechnology for high-performance and low-power logic transistor applications," *IEEE Trans. Nanotechnol.*, vol. 4, no. 2, pp. 153–158, Mar. 2005.

- [10] R. Chau, S. Datta, and A. Majumdar, "Opportunities and challenges of III–V nanoelectronics for future high-speed, low-power logic applications," in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp.*, Oct./Nov. 2005, pp. 17–20.

- [11] H. Riel, L.-E. Wernersson, M. Hong, and J. A. del Alamo, "III–V compound semiconductor transistors—From planar to nanowire structures," MRS Bull., vol. 39, no. 8, pp. 668–677, 2014.

- [12] W. Haensch et al., "Silicon CMOS devices beyond scaling," IBM J. Res. Develop., vol. 50, nos. 4–5, pp. 339–361, Jul. 2006.

$<sup>{}^{</sup>b}I_{on}$  is about 400  $\mu$ A/ $\mu$ m if extracted at  $V_{dd}$  = 0.5 V and  $I_{off}$  = 100 nA/ $\mu$ m.

- [13] T. N. Theis and P. M. Solomon, "In quest of the 'next switch': Prospects for greatly reduced power dissipation in a successor to the silicon field-effect transistor," *Proc. IEEE*, vol. 98, no. 12, pp. 2005–2014, Dec. 2010.

- [14] I. Ferain, C. A. Colinge, and J.-P. Colinge, "Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors," *Nature*, vol. 479, no. 7373, pp. 310–316, Nov. 2011.

- [15] R. S. Wagner and W. C. Ellis, "Vapor-liquid-solid mechanism of single crystal growth," *Appl. Phys. Lett.*, vol. 4, no. 5, p. 89, 1964.

- [16] S. A. Fortuna and X. Li, "Metal-catalyzed semiconductor nanowires: A review on the control of growth directions," *Semicond. Sci. Technol.*, vol. 25, no. 2, p. 024005, Feb. 2010.

- [17] L. E. Fröberg, W. Seifert, and J. Johansson, "Diameter-dependent growth rate of InAs nanowires," *Phys. Rev. B*, vol. 76, p. 153401, Oct. 2007.

- [18] A. W. Dey *et al.*, "High-performance InAs nanowire MOSFETs," *IEEE Electron Device Lett.*, vol. 33, no. 6, pp. 791–793, Jun. 2012.

- [19] A. C. Ford et al., "Diameter-dependent electron mobility of InAs nanowires," Nano Lett., vol. 9, no. 1, pp. 360–365, 2009.

- [20] A. Razavieh et al., "Effect of diameter variation on electrical characteristics of Schottky barrier indium arsenide nanowire field-effect transistors," ACS Nano, vol. 8, no. 6, pp. 6281–6287, 2014.

- [21] E. I. Givargizov, "Fundamental aspects of VLS growth," J. Crystal Growth, vol. 31, pp. 20–30, Dec. 1975.

- [22] K. Jung, P. K. Mohseni, and X. Li, "Ultrathin InAs nanowire growth by spontaneous Au nanoparticle spreading on indium-rich surfaces," *Nanoscale*, vol. 6, no. 24, pp. 15293–15300, 2014.

- [23] H. Schmid et al., "Patterned epitaxial vapor-liquid-solid growth of silicon nanowires on Si(111) using silane," J. Appl. Phys., vol. 103, no. 2, p. 024304, 2008.

- [24] L. E. Fröberg, C. Rehnstedt, C. Thelander, E. Lind, L.-E. Wernersson, and L. Samuelson, "Heterostructure barriers in wrap gated nanowire FETs," *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 981–983, Sep. 2008.

- [25] E. Lind, A. I. Persson, L. Samuelson, and L.-E. Wernersson, "Improved subthreshold slope in an InAs nanowire heterostructure field-effect transistor," *Nano Lett.*, vol. 6, no. 9, pp. 1842–1846, Sep. 2006.

- [26] X. Jiang, Q. Xiong, S. Nam, F. Qian, Y. Li, and C. M. Lieber, "InAs/InP radial nanowire heterostructures as high electron mobility devices," *Nano Lett.*, vol. 7, no. 10, pp. 3214–3218, Oct. 2007.

- [27] X. Miao, C. Zhang, and X. Li, "Monolithic barrier-all-around high electron mobility transistor with planar GaAs nanowire channel," *Nano Lett.*, vol. 13, no. 6, pp. 2548–2552, Jun. 2013.

- [28] L. C. Chuang, M. Moewe, C. Chase, N. P. Kobayashi, C. Chang-Hasnain, and S. Crankshaw, "Critical diameter for III–V nanowires grown on lattice-mismatched substrates," *Appl. Phys. Lett.*, vol. 90, no. 4, p. 043115, 2007.

- [29] E. P. A. M. Bakkers, M. T. Borgström, and M. A. Verheijen, "Epitaxial growth of III–V nanowires on group IV substrates," MRS Bull., vol. 32, no. 2, pp. 117–122, 2007.

- [30] P. Caroff, K. A. Dick, J. Johansson, M. E. Messing, K. Deppert, and L. Samuelson, "Controlled polytypic and twin-plane superlattices in III–V nanowires," *Nature Nanotechnol.*, vol. 4, no. 1, pp. 50–55, 2009.

- [31] H. J. Joyce et al., "Twin-free uniform epitaxial GaAs nanowires grown by a two-temperature process," Nano Lett., vol. 7, no. 4, pp. 921–926, 2007.

- [32] H. J. Joyce, J. Wong-Leung, Q. Gao, H. H. Tan, and C. Jagadish, "Phase perfection in zinc blende and wurtzite III–V nanowires using basic growth parameters," *Nano Lett.*, vol. 10, no. 3, pp. 908–915, 2010

- [33] K. A. Dick et al., "Control of III–V nanowire crystal structure by growth parameter tuning," Semicond. Sci. Technol., vol. 25, no. 2, p. 024009, 2010.

- [34] Q.-T. Do, K. Blekker, I. Regolin, W. Prost, and F. J. Tegude, "High transconductance MISFET with a single InAs nanowire channel," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 682–684, Aug. 2007.

- [35] C. Thelander, L. E. Fröberg, C. Rehnstedt, L. Samuelson, and L.-E. Wernersson, "Vertical enhancement-mode InAs nanowire fieldeffect transistor with 50-nm wrap gate," *IEEE Electron Device Lett.*, vol. 29, no. 3, pp. 206–208, Mar. 2008.

- [36] M. Egard *et al.*, "Vertical InAs nanowire wrap gate transistors with  $f_{\rm t} > 7$  GHz and  $f_{\rm max} > 20$  GHz," *Nano Lett.*, vol. 10, no. 3, pp. 809–812, Mar. 2010.

- [37] K.-M. Persson et al., "Extrinsic and intrinsic performance of vertical InAs nanowire MOSFETs on Si substrates," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2761–2767, Sep. 2013.

- [38] S. Johansson, E. Memisevic, L.-E. Wernersson, and E. Lind, "High-frequency gate-all-around vertical InAs nanowire MOSFETs on Si substrates," *IEEE Electron Device Lett.*, vol. 35, no. 5, pp. 518–520, May 2014.

- [39] J. A. del Alamo, private communication, 2015.

- [40] C. Thelander et al., "Development of a vertical wrap-gated InAs FET," IEEE Trans. Electron Devices, vol. 55, no. 11, pp. 3030–3036, Nov. 2008.

- [41] S. A. Fortuna, J. Wen, I. S. Chun, and X. Li, "Planar GaAs nanowires on GaAs (100) substrates: Self-aligned, nearly twin-defect free, and transfer-printable," *Nano Lett.*, vol. 8, no. 12, pp. 4421–4427, Dec. 2008.

- [42] R. Dowdy, D. A. Walko, S. A. Fortuna, and X. Li, "Realization of unidirectional planar GaAs nanowires on GaAs (110) substrates," *IEEE Electron Device Lett.*, vol. 33, no. 4, pp. 522–524, Apr. 2012.

- [43] R. S. Dowdy, D. A. Walko, and X. Li, "Relationship between planar GaAs nanowire growth direction and substrate orientation," *Nanotechnology*, vol. 24, no. 3, p. 035304, Jan. 2013.

- [44] C. Zhang, X. Miao, P. K. Mohseni, W. Choi, and X. Li, "Site-controlled VLS growth of planar nanowires: Yield and mechanism," *Nano Lett.*, vol. 14, no. 12, pp. 6836–6841, Dec. 2014.

- [45] S. A. Fortuna and X. Li, "GaAs MESFET with a high-mobility self-assembled planar nanowire channel," *IEEE Electron Device Lett.*, vol. 30, no. 6, pp. 593–595, Jun. 2009.

- [46] C. Zhang and X. Li, "Planar GaAs nanowire tri-gate MOSFETs by vapor-liquid-solid growth," *Solid-State Electron.*, vol. 93, pp. 40–42, Mar. 2014.

- [47] C. Zhang, R. Dowdy, and X. Li, "High voltage gain MESFET amplifier using self-aligned MOCVD grown planar GaAs nanowires," in *Proc. Annu. Device Res. Conf. (DRC)*, Jun. 2013, pp. 63–64.

- [48] X. Miao, K. Chabak, C. Zhang, P. K. Mohseni, D. A. Walko, and X. Li, "High-speed planar GaAs nanowire arrays with f<sub>max</sub> > 75 GHz by wafer-scale bottom-up growth," *Nano Lett.*, vol. 15, no. 4, pp. 2780–2786, 2015.

- [49] C. Zhang, W. Choi, P. K. Mohseni, and X. Li, "InAs planar nanowire gate-all-around MOSFETs on GaAs substrates by selective lateral epitaxy," *IEEE Electron Device Lett.*, vol. 36, no. 7, pp. 663–665, Jul. 2015.

- [50] J. J. Coleman, R. M. Lammert, M. Osowski, and A. Jones, "Progress in InGaAs-GaAs selective-area MOCVD toward photonic integrated circuits," *IEEE J. Sel. Topics Quantum Electron.*, vol. 3, no. 3, pp. 874–884, Jun. 1997.

- [51] K. Tomioka, M. Yoshimura, and T. Fukui, "A III–V nanowire channel on silicon for high-performance vertical transistors," *Nature*, vol. 488, no. 7410, pp. 189–192, Aug. 2012.

- [52] T. Tanaka, K. Tomioka, S. Hara, J. Motohisa, E. Sano, and T. Fukui, "Vertical surrounding gate transistors using single InAs nanowires grown on Si substrates," *Appl. Phys. Exp.*, vol. 3, no. 2, p. 025003, Jan. 2010.

- [53] K. Tomioka, M. Yoshimura, E. Nakai, F. Ishizaka, and T. Fukui, "Integration of III-V nanowires on Si: From high-performance vertical FET to steep-slope switch," in *IEDM Tech. Dig.*, Dec. 2013, pp. 4.1.1–4.1.4.

- [54] J. Motohisa, J. Noborisaka, J. Takeda, M. Inari, and T. Fukui, "Catalyst-free selective-area MOVPE of semiconductor nanowires on (111)B oriented substrates," *J. Crystal Growth*, vol. 272, nos. 1–4, pp. 180–185, Dec. 2004.

- [55] K. Tomioka, J. Motohisa, S. Hara, and T. Fukui, "Control of InAs nanowire growth directions on Si," *Nano Lett.*, vol. 8, no. 10, pp. 3475–3480, Oct. 2008.

- [56] Y. Song et al., "III-V junctionless gate-all-around nanowire MOSFETs for high linearity low power applications," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 324–326, Mar. 2014.

- [57] J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon, and P. D. Ye, "First experimental demonstration of gate-all-around III–V MOSFETs by top-down approach," in *IEDM Tech. Dig.*, Dec. 2011, pp. 33.2.1–33.2.4.

- [58] J. J. Gu et al., "20–80 nm channel length InGaAs gate-all-around nanowire MOSFETs with EOT=1.2 nm and lowest SS=63 mV/dec," in *IEDM Tech. Dig.*, Dec. 2012, pp. 27.6.1–27.6.4.

- [59] J. J. Gu et al., "III-V gate-all-around nanowire MOSFET process technology: From 3D to 4D," in *IEDM Tech. Dig.*, Dec. 2012, pp. 23.7.1–23.7.4.

- [60] X. Zhao, J. Lin, E. A. Fitzgerald, and J. A. del Alamo, "Vertical nanowire InGaAs MOSFETs fabricated by a top-down approach," in *IEDM Tech. Dig.*, Dec. 2013, pp. 28.4.1–28.4.4.

- [61] X. Zhao and J. A. del Alamo, "Nanometer-scale vertical-sidewall reactive ion etching of InGaAs for 3-D III-V MOSFETs," *IEEE Electron Device Lett.*, vol. 35, no. 5, pp. 521–523, May 2014.

- [62] J. Lin, X. Zhao, D. A. Antoniadis, and J. A. del Alamo, "A novel digital etch technique for deeply scaled III-V MOSFETs," *IEEE Electron Device Lett.*, vol. 35, no. 4, pp. 440–442, Apr. 2014.

- [63] S. Lee et al., "Record extrinsic transconductance (2.45 mS/μm at VDS = 0.5 V) InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel MOSFETs using MOCVD source-drain regrowth," in Proc. Symp. VLSI Technol., Jun. 2013, pp. T246–T247.

- [64] A. Alian, C. Merckling, G. Brammertz, M. Meuris, M. Heyns, and K. D. Meyer, "InGaAs MOS transistors fabricated through a digitaletch gate-recess process and the influence of forming gas anneal on their electrical behavior," ECS J. Solid State Sci. Technol., vol. 1, no. 6, pp. P310–P314, Oct. 2012.

- [65] International Technology Roadmap for Semiconductors (ITRS) Report, 2013 Edition. [Online]. Available: http://www.itrs.net, accessed Int. 2015

- [66] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFET's," *IEEE Electron Device Lett.*, vol. 18, no. 2, pp. 74–76, Feb. 1997.

- [67] B. Yu, Y. Yuan, P. M. Asbeck, and Y. Taur, "Scaling of nanowire transistors," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp. 2846–2858, Nov. 2008.

- [68] F. Wang et al., "The scaling of the effective band gaps in indiumarsenide quantum dots and wires," ACS Nano, vol. 2, no. 9, pp. 1903–1913, 2008.

- [69] J. Li and L.-W. Wang, "Band-structure-corrected local density approximation study of semiconductor quantum dots and wires," *Phys. Rev. B*, vol. 72, no. 12, p. 125325, Sep. 2005.

- [70] E. Lind, M. P. Persson, Y.-M. Niquet, and L.-E. Wernersson, "Band structure effects on the scaling properties of [111] InAs nanowire MOSFETs," *IEEE Trans. Electron Devices*, vol. 56, no. 2, pp. 201–205, Feb. 2009.

- [71] K. Alam and R. N. Sajjad, "Electronic properties and orientation-dependent performance of InAs nanowire transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 11, pp. 2880–2885, Nov. 2010.

- [72] C. L. dos Santos and P. Piquini, "Diameter dependence of mechanical, electronic, and structural properties of InAs and InP nanowires: A firstprinciples study," *Phys. Rev. B*, vol. 81, no. 7, p. 075408, Feb. 2010.

- [73] Y. Taur, "An analytical solution to a double-gate MOSFET with undoped body," *IEEE Electron Device Lett.*, vol. 21, no. 5, pp. 245–247, May 2000.

- [74] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, U.K.: Cambridge Univ. Press, 1998.

- [75] M. Si et al., "Effects of forming gas anneal on ultrathin InGaAs nanowire metal-oxide-semiconductor field-effect transistors," Appl. Phys. Lett., vol. 102, no. 9, p. 093505, 2013.

- [76] K. Tomioka, M. Yoshimura, and T. Fukui, "Vertical In<sub>0.7</sub>Ga<sub>0.3</sub>As nanowire surrounding-gate transistors with high-k gate dielectric on Si substrate," in *IEDM Tech. Dig.*, Dec. 2011, pp. 33.3.1–33.3.4.

- [77] S. Sasaki et al., "Encapsulated gate-all-around InAs nanowire field-effect transistors," Appl. Phys. Lett., vol. 103, no. 21, p. 213502, 2013.

- [78] T. Bryllert, L.-E. Wernersson, L. E. Fröberg, and L. Samuelson, "Vertical high-mobility wrap-gated InAs nanowire transistor," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 323–325, May 2006.

- [79] K.-M. Persson *et al.*, "Vertical InAs nanowire MOSFETs with IDS = 1.34 mA/μm and gm = 1.19 mS/μm at VDS = 0.5 V," in *Proc. 70th Annu. Device Res. Conf. (DRC)*, Jun. 2012, pp. 195–196.

- [80] Y. Xuan, H. C. Lin, P. D. Ye, and G. D. Wilk, "Capacitance-voltage studies on enhancement-mode InGaAs metal-oxide-semiconductor field-effect transistor using atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> gate dielectric," Appl. Phys. Lett., vol. 88, no. 26, p. 263518, 2006.

- [81] Y. B. Kim, M. S. Kang, D. K. Choi, T. Lee, and J. Ahn, "Physical and electrical properties of atomic layer deposited HfO<sub>2</sub> for gate dielectric application," *J. Korean Phys. Soc.*, vol. 42, pp. S1146–S1148, Apr. 2003.

- [82] Y. Xuan, Y. Q. Wu, H. C. Lin, T. Shen, and P. D. Ye, "Submicrometer inversion-type enhancement-mode InGaAs MOSFET with atomiclayer-deposited Al<sub>2</sub>O<sub>3</sub> as gate dielectric," *IEEE Electron Device Lett.*, vol. 28, no. 11, pp. 935–938, Nov. 2007.

- [83] Y. Xuan, T. Shen, M. Xu, Y. Q. Wu, and P. D. Ye, "High-performance surface channel In-rich In<sub>0.75</sub>Ga<sub>0.25</sub>As MOSFETs with ALD high-k as gate dielectric," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [84] P. D. Ye, "Main determinants for III-V metal-oxide-semiconductor field-effect transistors (invited)," J. Vac. Sci. Technol. A, vol. 26, no. 4, p. 697, 2008.

- [85] J. J. Gu, A. T. Neal, and P. D. Ye, "Effects of (NH<sub>4)2</sub>S passivation on the off-state performance of 3-dimensional InGaAs metal-oxidesemiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 99, no. 15, p. 152113, 2011.

- [86] M. Radosavljevic et al., "Non-planar, multi-gate InGaAs quantum well field effect transistors with high-K gate dielectric and ultra-scaled gateto-drain/gate-to-source separation for low power logic applications," in IEDM Tech. Dig., Dec. 2010, pp. 6.1.1–6.1.4.

- [87] C. W. Wilmsen, "The MOS/InP interface," *Critical Rev. Solid State Sci.*, vol. 5, no. 3, pp. 313–317, Oct. 1975.

- [88] D. L. Lile and D. A. Collins, "An InP MIS diode," Appl. Phys. Lett., vol. 28, no. 9, p. 554, 1976.

- [89] S. Kundu, N. N. Halder, D. Biswas, P. Banerji, T. Shripathi, and S. Chakraborty, "Role of ultra thin pseudomorphic InP layer to improve the high-k dielectric/GaAs interface in realizing metal-oxidesemiconductor capacitor," *J. Appl. Phys.*, vol. 112, no. 3, p. 034514, 2012

- [90] M. Xu et al., "New insight into Fermi-level unpinning on GaAs: Impact of different surface orientations," in *IEDM Tech. Dig.*, Dec. 2009, pp. 1–4.

- [91] D.-G. Park, Z. Chen, A. E. Botchkarev, S. N. Mohammad, and H. Morkoç, "Interface properties of Si<sub>3</sub>N<sub>4</sub>/Si/n-GaAs metal-insulatorsemiconductor structure using a Si interlayer," *Philos. Mag. B*, vol. 74, no. 3, pp. 219–234, Sep. 2006.

- [92] S. Tiwari, S. L. Wright, and J. Batey, "Unpinned GaAs MOS capacitors and transistors," *IEEE Electron Device Lett.*, vol. 9, no. 9, pp. 490–499, Sep. 1988.

- [93] D.-G. Park, D. M. Diatezua, Z. Chen, S. N. Mohammad, and H. Morkoç, "Characteristics of Si<sub>3</sub>N<sub>4</sub>/Si/n-GaAs metal-insulatorsemiconductor interfaces grown on GaAs(111)B substrate," *Appl. Phys. Lett.*, vol. 69, no. 20, p. 3025, 1996.

- [94] Z. Wang, D. S. L. Mui, A. L. Demirel, D. Biswas, J. Reed, and H. Morkoç, "Gate quality Si<sub>3</sub>N<sub>4</sub>/Si/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-insulatorsemiconductor capacitors," *Appl. Phys. Lett.*, vol. 61, no. 15, p. 1826, 1992.

- [95] C. L. Hinkle *et al.*, "Detection of Ga suboxides and their impact on III–V passivation and Fermi-level pinning," *Appl. Phys. Lett.*, vol. 94, no. 16, p. 162101, 2009.

- [96] M. Lundstrom, "Elementary scattering theory of the Si MOSFET," IEEE Electron Device Lett., vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [97] F. Wang et al., "Surface roughness induced electron mobility degradation in InAs nanowires," Nanotechnology, vol. 24, no. 37, p. 375202, Sep. 2013.

- [98] J. J. Hou et al., "Diameter dependence of electron mobility in InGaAs nanowires," Appl. Phys. Lett., vol. 102, no. 9, p. 093112, 2013.

- [99] M. Scheffler, S. Nadj-Perge, L. P. Kouwenhoven, M. T. Borgström, and E. P. A. M. Bakkers, "Diameter-dependent conductance of InAs nanowires," *J. Appl. Phys.*, vol. 106, no. 12, p. 124303, 2009.

- [100] N. Gupta et al., "Temperature-dependent electron mobility in InAs nanowires," *Nanotechnology*, vol. 24, no. 22, p. 225202, Jun. 2013.

- [101] J. W. W. van Tilburg, R. E. Algra, W. G. G. Immink, M. Verheijen, E. P. A. M. Bakkers, and L. P. Kouwenhoven, "Surface passivated InAs/InP core/shell nanowires," *Semicond. Sci. Technol.*, vol. 25, no. 2, p. 024011, Feb. 2010.

- [102] C. R. Bolognesi, H. Kroemer, and J. H. English, "Well width dependence of electron transport in molecular-beam epitaxially grown InAs/AlSb quantum wells," *J. Vac. Sci. Technol. B*, vol. 10, no. 2, pp. 877–879, 1992.

- [103] J. J. Gu, H. Wu, Y. Liu, A. T. Neal, R. G. Gordon, and P. D. Ye, "Size-dependent-transport study of In<sub>0.53</sub>Ga<sub>0.47</sub>As gate-all-around nanowire MOSFETs: Impact of quantum confinement and volume inversion," *IEEE Electron Device Lett.*, vol. 33, no. 7, pp. 967–969, Jul. 2012.

- [104] S. D. Suk et al., "Investigation of nanowire size dependency on TSNWFET," in IEDM Tech. Dig., Dec. 2007, pp. 891–894.

- [105] M.-H. Na, E. J. Nowak, W. Haensch, and J. Cai, "The effective drive current in CMOS inverters," in *IEDM Tech. Dig.*, Dec. 2002, pp. 121–124.

- [106] D.-H. Kim and J. A. del Alamo, "Scalability of sub-100 nm InAs HEMTs on InP substrate for future logic applications," *IEEE Trans. Electron Devices*, vol. 57, no. 7, pp. 1504–1511, Jul. 2010.

- [107] S. Birner et al., "nextnano: General purpose 3-D simulations," IEEE Trans. Electron Devices, vol. 54, no. 9, pp. 2137–2142, Sep. 2007.

- [108] C. Auth et al., "A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," in Tech. Dig. Symp. VLSI Technol., Jun. 2012, pp. 131–132.

- [109] S. Narasimha *et al.*, "22 nm high-performance SOI technology featuring dual-embedded stressors, epi-plate high-*K* deep-trench embedded DRAM and self-aligned via 15 LM BEOL," in *IEDM Tech. Dig.*, Dec. 2012, pp. 3.3.1–3.3.4.

- [110] S. Bangsaruntip et al., "Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond," in *IEDM Tech. Dig.*, Dec. 2013, pp. 20.2.1–20.2.4.

- [111] R. Kim, U. E. Avci, and I. A. Young, "Source/drain doping effects and performance analysis of ballistic III–V n-MOSFETs," *IEEE J. Electron Devices Soc.*, vol. 3, no. 1, pp. 37–43, Jan. 2015.

- [112] S. Lee et al., "Record  $I_{on}$  (0.50 mA/ $\mu$ m at  $V_{DD} = 0.5$  V and  $I_{off} = 100$  nA/ $\mu$ m) 25 nm-gate-length ZrO<sub>2</sub>/InAs/InAlAs MOSFETs," in Symp. VLSI Technol. Dig. Tech. Papers, Jun. 2014, pp. 1–2.

- pp. 1–2.

[113] S. Natarajan *et al.*, "A 14 nm logic technology featuring 2<sup>nd</sup>-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 μm<sup>2</sup> SRAM cell size," in *Proc. IEEE IEDM*, Dec. 2014, pp. 3.7.1–3.7.3.

- [114] N. Kharche, G. Klimeck, D.-H. Kim, J. A. del Alamo, and M. Luisier, "Multiscale metrology and optimization of ultra-scaled InAs quantum well FETs," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 1963–1971, Jul. 2011.

Chen Zhang received the B.S. and M.S. degrees in electronic engineering from Tsinghua University, Beijing, China, in 2007 and 2010, respectively, and the Ph.D. degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign, Urbana, IL, USA, in 2015.

He is currently with IBM Research, Albany, NY, USA. His thesis research involves the growth and fabrication of III-V nanowire transistors and MOSFET device physics.

**Xiuling Li** received the B.S. degree from Peking University, Beijing, China, and the Ph.D. degree from the University of California at Los Angeles, Los Angeles, CA, USA.

She joined the University of Illinois at Urbana-Champaign, Urbana, IL, USA, in 2007, and is currently a Professor with the Department of Electrical and Computer Engineering. Her current research interests include nanostructured semiconductor materials and devices.